Running STING on PULPino Platform

PULPino is a competitive, state-of-the-art 32-bit processor based on the RISC-V architecture, with a rich set of peripherals, and full debug support developed at ETH Zurich and Università di Bologna. PULPino is based on optimized 32-bit RISC-V cores (known as RI5CY and Zero-riscy) with complete support for the RV32I base integer instruction set and extensions for compressed and integer multiplication/division instructions. The core also implements several other custom extensions such as - hardware loops, post incrementing load and store instructions, ALU and MAC operations. A very small subset of privileged specification and CSR (control and status registers) has been implemented to keep the footprint of the core as small as possible. More information on the implementation can be found in the PULPino documentation.

Enabling STING on PULPino

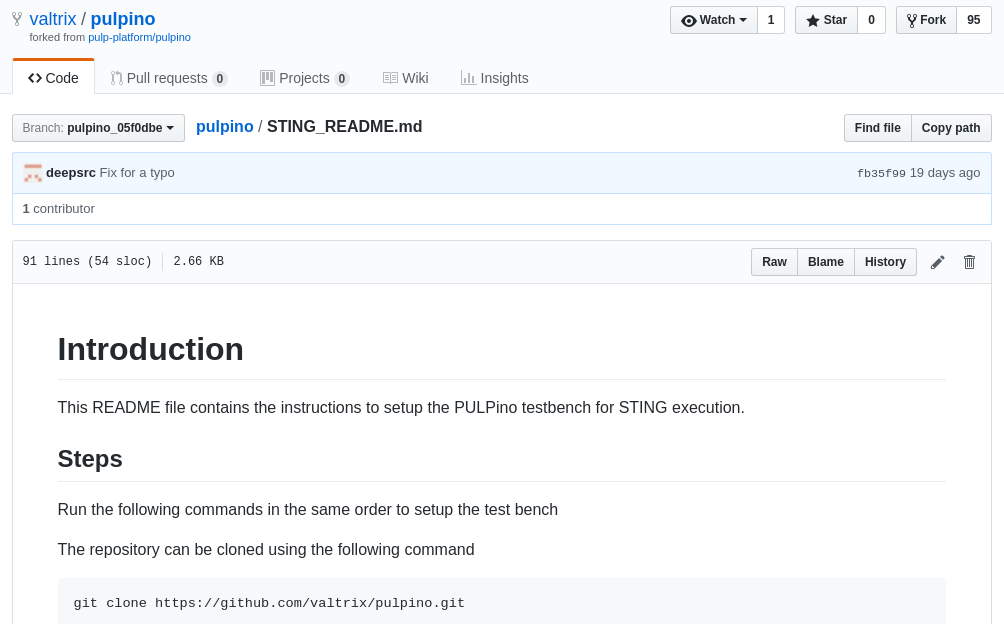

We recently enabled STING on the open source test bench of PULPino available in the project’s github repository. The code base has been forked so that STING specific customizations can be added as required. The steps to setup the test bench and run STING binaries are documented in a README file which can be found here (snapshot below).

Minor modifications to the test bench were made (e.g. relocating ROM, combining instruction and data memory into a single memory block) to get STING up and running on the platform. The size of the RAM was also increased to ensure that more number of tests could be packed in a single STING binary.

On the tool side, support for some of the custom extensions (hardware loops) and PULPino peripherals (timer, UART, event unit etc.) was added to support the design verification needs of the platform.

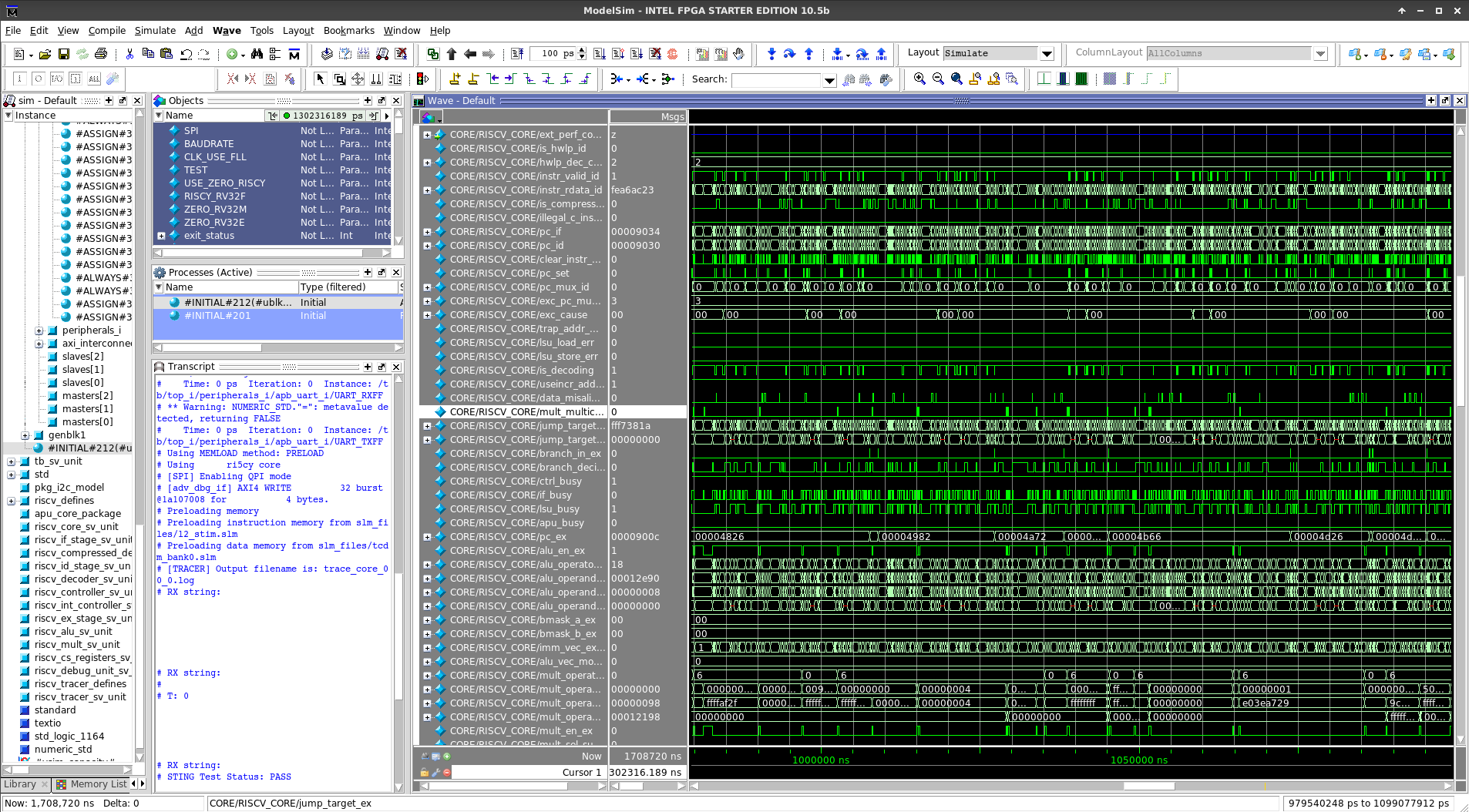

Running STING on PULPino Simulations

The steps to run the STING test can be found in the README file. A STING binary has been copied to the following path - sw/apps/sting/images in the forked repository. It can be used to run and evaluate a test comprising of random stimulus on the PULPino simulations.

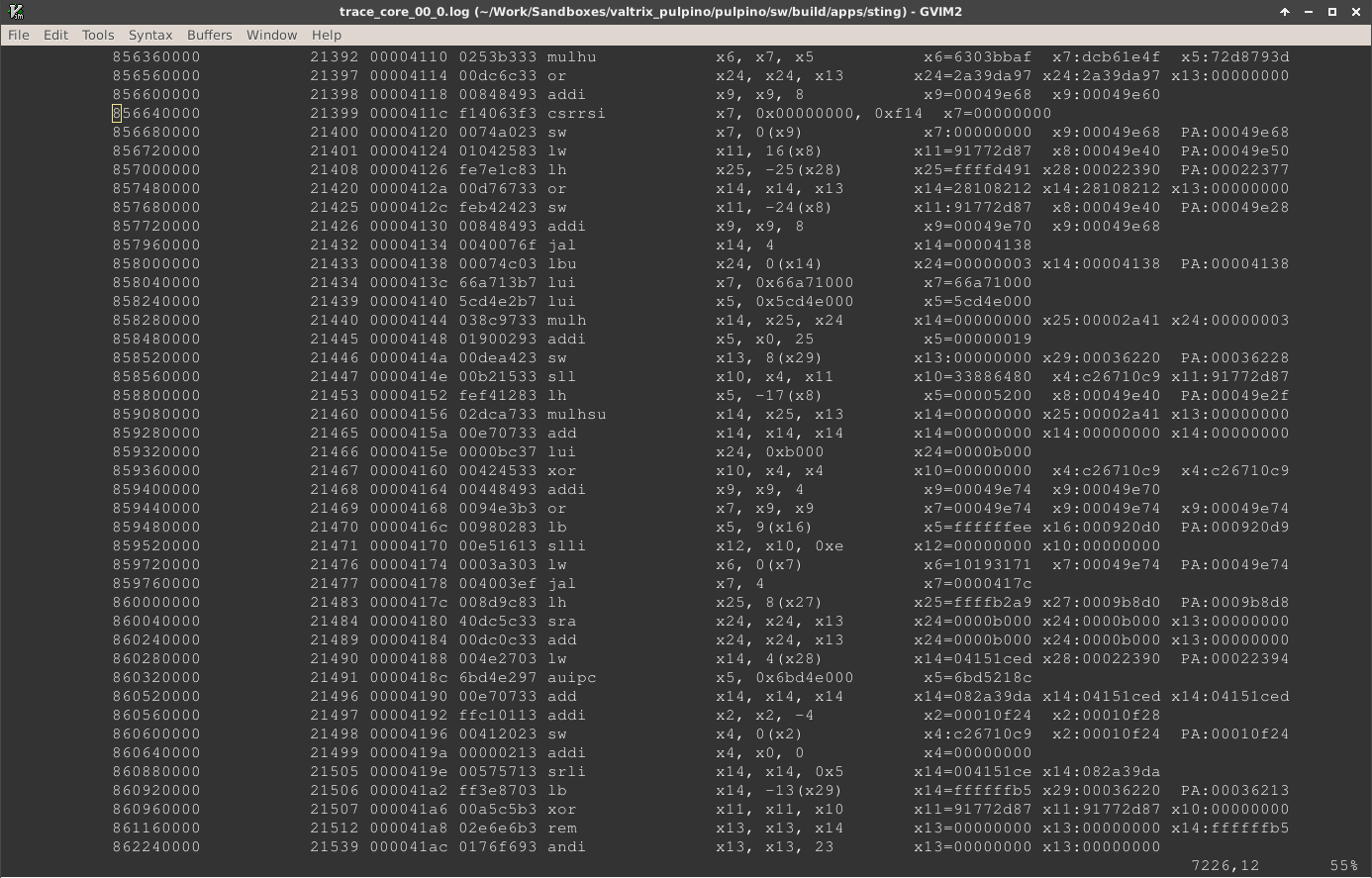

Once the test is run, the waves and core trace are dumped in - sw/build/apps/sting. Snapshot of the core trace from the STING test is given below.

Conclusion

STING has been successfully ported to the specifications of the PULPino platform and can be extended further to meet the verification needs of any SoC/IP design based on it.

We have plans to run STING extensively on PULPino and make sure that the design is compliant with the RISC-V specification. The test stimulus will be a random mix of instructions supported by the PULPino core, the bias for which can be controlled using configuration files. In addition to the random test content, a large number of focused and corner-case scenarios are also covered using snippets of directed code. The timer, UART and event unit devices are also programmed for concurrency and to allow generation of interrupts at regular intervals during the test execution. The results from test execution on PULPino simulations are compared with the results obtained from running the same test on SPIKE (the RISC-V CPU model) to ensure functionally correct behavior.

If this interests you, write to contact@valtrix.in to know how STING can help meet your RISC-V verification goals quickly and efficiently.

Categories: programming

Subscribe

Subscribe to this blog via RSS.

Categories

General 5

Reports 1

Recent Posts

Importance of Software Driven Functional Verification Methodology

Posted on 05 Sep 2020Using STING Release Packages for Verifying RISC-V Implementations

Posted on 25 Oct 2019